새로운소식

학과의 최신 소식과 활동을 전해드립니다.

김창현(석사과정), 대한전자공학회 하계종합학술대회 “우수논문상” 수상

포스텍 전자전기공학과 석사과정 김창현 학생(지도교수: 이영주)이 8/19~8/21 제주에서 개최된 대한전자공학회 2020년도 하계종합학술대회에서 우수논문상(네이버 논문상)을 수상하였다. (공동수상: 감동윤 박사과정, 이영주 교수)

연구팀은 ETRI와의 공동 연구를 통하여 공장자동화용 IoT 통신 시스템을 개발하고 있으며, “짧은 오류정정부호를 위한 OSD 알고리즘의 복잡도 분석”이라는 논문에서 세계 최초로 이론적 수준에서 개발되고 있는 차세대 OSD기반 오류정정부호의 구현 복잡도를 5G 상용 시스템과 비교분석 하였다. 이를 바탕으로 향후 관련 분야의 실용화를 위한 연구 방향을 제시, 그 우수성을 높게 평가받았다.

POSTECH 전자전기공학과 비전임교수 초빙

POSTECH 전자전기공학과 비전임교수 초빙

(전자전기공학 분야)

포항공과대학교 (POSTECH) 전자전기공학과에서는 산학연의 원활한 정보교환 및 긴 밀한 협력체계 구축을 위하여 타기관에 소속된 인사를 비전임교원으로 초빙합니다.

1. 초빙분야 및 인원

제어 및 전력전자 분야 전공자 / 0명

2. 계약 조건

– 직위: 겸직교원 (비전임교원)

– 계약기간: 2년, 재임용 가능

– 업무: 포스텍 전자전기공학과 제어 및 전력전자분야의 산학협동연구활성화

3. 임용 예정일 : 2020년 12월 1일

4. 지원자격

– 사립학교 교원임용에 결격사유가 없는 초빙 분야 관련 박사학위 소지한 분

– 박사학위 취득 후 철강계측제어 산학협력 분야 경력 10년 이상

5. 제출서류 및 심사

가. 1차 서류 심사

– 이력서 (자율 서식, 논문 및 저서목록 포함)

– 자기소개서 (자율 서식)

– 경력증명서 또는 재직증명서

– 최종학위증명서

나. 2차 면접 심사

– 1차 서류심사 통과자에 한하여 면접 심사 또는 공개강의 실시

6. 서류 접수

– 1차 서류 마감: 2020년 9월 7일 (금), 11:59pm

– 서류접수: 아래 문의처 메일로 위 5-가. 서류를 pdf 형식으로 송부

7. 기타

– 제출서류는 반환하지 않으며, 기재내용이 사실과 다를 경우 임용이 취소됩니다.

– 문의처: 전자전기공학과 황미정 (054-279-2718, mjhwang@postech.ac.kr)

[(주)다이얼로그 세미컨덕터 코리아] 전문연구 요원 채용 공고

<회사 소개>

Dialog Semiconductor Korea 외국계기업 7F, SiliconPark, 35, Pangyo-ro 255beon-gil, Bundang-gu,Seongnam-si, Gyeonggi-do, Korea (Zip code : 463-400)

https://www.dialog-semiconductor.com/

Dialog Semiconductor is a leading provider of custom, highly-integrated and Digital Design Engineer_Job_Posting_200709configurable mixed-signal ICs, backed by world-class manufacturing partners. We are a socially responsible employer pursuing programs that benefit our employees, stakeholders and community.

Dialog’s custom power management, configurable mixed-signal and highly-integrated connectivity ICs deliver outstanding efficiency, flexibility and performance advantages. Dialog’s ICs make it possible to develop the next generation of smart devices for consumers and businesses by enhancing product functionality, accelerating the pace of innovation and powering the smart connected future.

Dialog has a renowned reputation for flexible, dynamic support and world-class innovation. The world’s leading electronics manufacturers and suppliers trust Dialog to deliver, thanks to our decades of experience as an established business partner in the rapid development of custom ICs.

Dialog operates a fabless business model and is a socially responsible employer pursuing many programs to benefit the employees, community, other stakeholders and the environment we operate in. Dialog Semiconductor plc is headquartered in London with a global sales, R&D and marketing organization. In 2018, it had US$1.442 billion in revenue and was one of the fastest growing European public semiconductor companies. It currently has approximately 2,100 employees worldwide. The company is listed on the Frankfurt (FWB: DLG) stock exchange (Regulated Market, Prime Standard, ISIN GB0059822006) and is a member of the German TecDax index.

For more information, visit www.dialog-semiconducr.com

<채용 공고>

https://www.peoplenjob.com/jobs/4158141?field=all&period=all&q=dialog

Job Description

As part of our continued growth, we seek Digital Design Engineer to work as an ASIC RTL design engineer.

Good knowledge in design techniques and low power logic design. Good knowledge in architectures of CPU subsystem,

especially ARM CPUs and AMBA subsystem, digital interfaces, and various digital components. Working in Digital CDT or

PDT or MDT, IoT Wi-Fi BU Team based in Pangyo, Korea you will:

The Role

Working in Digital CDT or PDT or MDT, IoT Wi-Fi BU Team based in Pangyo, Korea you will:

- RTL design and simulation verification of

- CPU subsystem, especially using ARM CPU and AMBA subsystem architecture

- Various digital interfaces such as I2C, SPI, UART, PWM, SDIO, eMMC, GPIO, etc

- Various digital components such as FIFO, DMA, timers, memory controllers, cache controller, etc

- FPGA design and verification (Xilinx or Intel)

- DFT (Design For Testability)

- ASIC top

- Digital front-end jobs interfacing with layout engineers

- Design and verification of digital modem design in terms of algorithm and RTL

- Design and verification of security and cryptographic components in terms of algorithm and RTL

- Collaboration with various kinds of people such as system architects, software engineers, verification engineers, RF/analog design engineers, etc

- Documentations on everything one did.

Job Requirements

What We Are Looking For?

Essential

- MS or PHD in Electrical/Electronic Engineering

- Majoring in or experiencing

- HDL language such as Verilog, System Verilog, VHDL, etc

- EDA tools such as Cadence’s Virtuoso, Xcelium/Incisive/Simvision, Synopsys’ Design Compiler, PrimeTime, Test Compiler, Synplify, etc

- RTL design including creating good test benches

Design of some of CPU subsystems, especially using ARM CPUs and AMBA components

- Design of some of digital interfaces such as I2C, SPI, UART, PWM, SDIO, eMMC, GPIO, etc

- Design of some of digital components such as FIFO, DMA, timers, memory controllers, cache controller, etc

- Some of FPGA design (Xilinx or Intel)

- Having good skill in UNIX, C/C++, and scripting languages like Tcl

- Having good communication skill in collaborating with other people

- Taking aggressive approach to meet the own development plan

Desirable

- Understand the overall application of the chips and developing improved design

- Majoring in or experiencing

- Digital front-end

- Soc tape-out

- Design of wide range of CPU subsystems, especially using arm CPUs and amba components

- Design of wide range of digital interfaces such as i2c, SPI, UART, PWM, SDIO, eMMC, GPIO, etc

- Design of wide range of digital components such as FIFO, DMA, timers, memory controllers, cache controller, etc

- Extensive FPGA design (Xilinx or Intel)

- Majoring in or experiencing digital signal processing

- Majoring in or experiencing digital modem design in terms of algorithm and RTL design

- Majoring in or experiencing security and cryptography in terms of theory and RTL design

- Having good skill in Matlab or System C

Additional Information

커리어수준 : 학생/신입

급여사항 : Discuss after interview

고용형태 : 정규직

경력여부 : 경력 Guidelines for Applicants

전형방법 : 1st. Document screening

2nd. Interview

제출서류 : Korean resume, English resume, Korean self introduction letter (Proof of documents must be submitted upon request

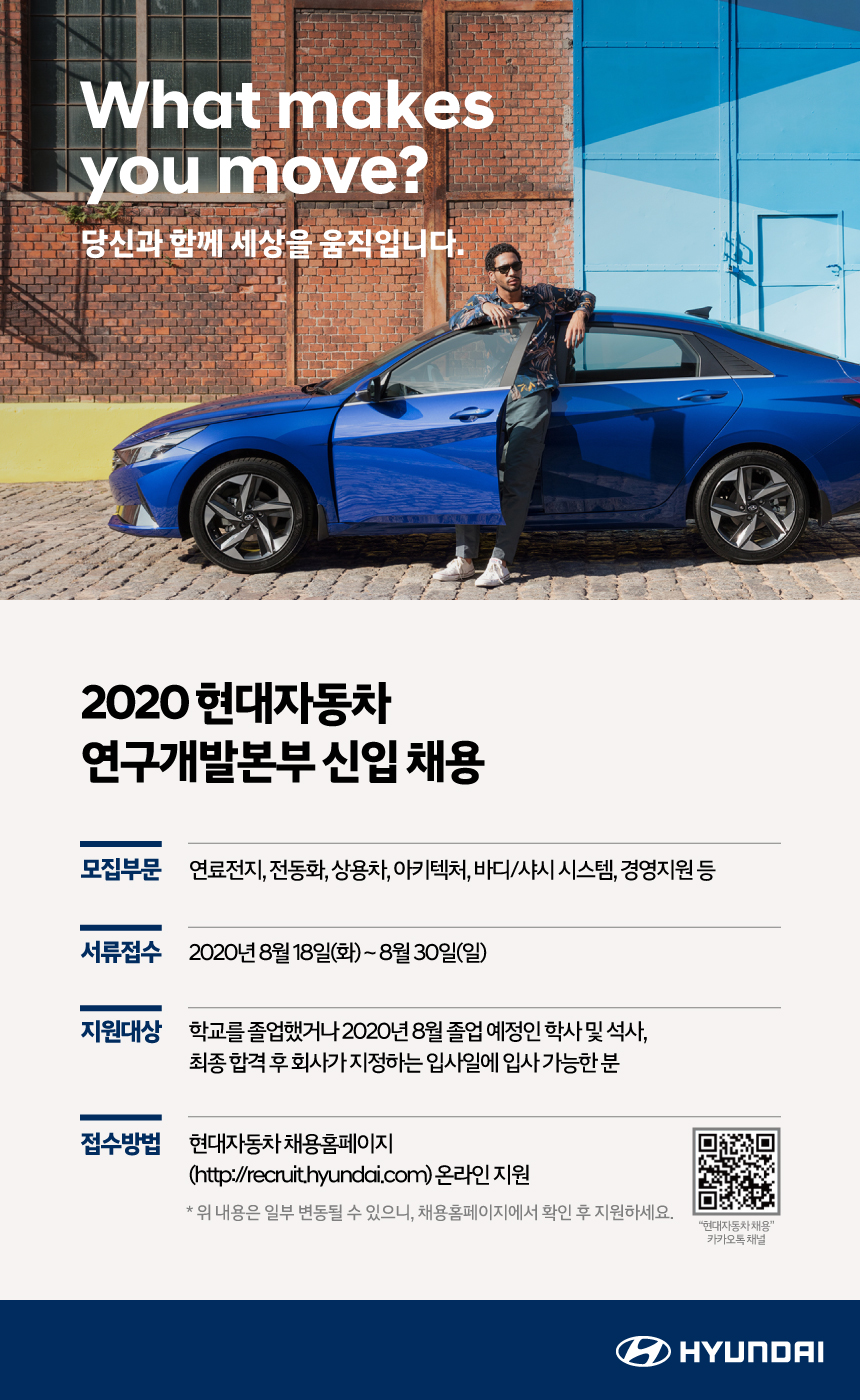

[현대자동차] 2020 현대자동차 연구개발본부 신입 상시 채용(~8.30/일)

What makes you move?

2020 현대자동차 연구개발본부 신입 상시 채용

■ 모집부문:

연료전지, 전동화, 상용차, 아키텍처, 바디/샤시 시스템,경영지원 등

■ 서류접수:

‘20년8월18일(화)~8월30일(일)

■ 지원대상:

학교를 졸업했거나2020년8월 졸업 예정인 학사 및 석사,

최종합격 후 회사가 지정하는 입사일에 입사 가능한 분

*공고별수행직무,자격요건 등 상세 내용은 채용 홈페이지에서 공고 확인 후 지원해주시기 바랍니다

▶현대자동차 카카오톡 채널 추가하기

카카오톡 채널을 추가하시면 앞으로 진행되는 현대자동차의 채용 소식을 카카오톡을 통해 받아 보실 수 있습니다.

■ 접수방법:

현대자동차 채용홈페이지 온라인 지원(http://recruit.hyundai.com/)

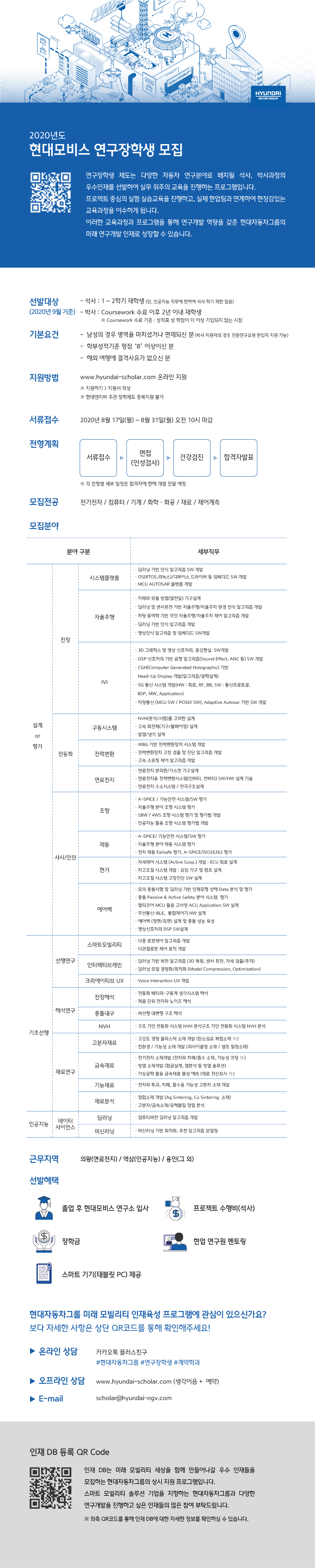

[현대자동차그룹] 현대모비스 연구장학생/계약학과 모집 (~08.31/월 오전10시)

2020 [현대자동차그룹] 현대모비스 연구장학생/계약학과 선발

■ 모집부문:

1) 연구장학생 : 현대모비스

※ 현대자동차, 현대제철 연구장학생 9월 모집예정

(회사별 중복 지원 불가)

2) http://hmg-scholar.com/ 연구장학생관련 상세 페이지

■ 서류접수:

20년 8월 17일(월)~8월31일(월)

■ 모집대상:

1) 석사 : 1 ~ 2학기 재학생

(단, 인공지능 직무에 한하여 석사 학기 제한 없음)

2) 박사 : Coursework 수료 이후 2년 이내 (박사/석박통합 공통)

※ Coursework 수료 기준

– 성적표 상 학점이 더이상 기입되지 않는 시점

■ 근무지역:

의왕(연료전지) / 역삼(인공지능) / 용인(그 외)

■ 선발전공:

전기전자/ 컴퓨터 / 기계 / 화학,화공 / 재료 / 제어계측

■ 선발혜택:

채용 연계, 장학금, 스마트기기(태블릿 PC) 제공, 프로젝트 수행비(석사), 현업 연구언 멘토링

■ 지원방법:

1) http://www.hyundai-scholar.com 온라인 지원

▶ 현대자동차그룹 연구장학생 온라인 상담 (카카오톡 플러스 친구)

모집 기간 내 상시 운영 : 09:00~17:00 (*주말 및 공휴일 제외)

홍원빈 교수, “이달의 과학기술인상” 수상

오태현 교수, CVPR2020 “Outstanding Reviewer Award” 수상

포스텍 전자전기공학과 오태현 교수가 “IEEE/CVF Conference on Computer Vision and Pattern Recognition (CVPR), 2020”에서 Outstanding Reviewer Award를 수상하였다.

본 상은 과거 Best Reviewer Awards 에 해당하는 것으로 오 교수는 CVPR 2020 전체 논문 평가자 3,664명 가운데 선별된 Outstanding Reviewers 중 한 명으로 선정되었다.

IEEE/CVF CVPR 학회는 인공지능 (AI) 분야에서 최고 학회 중 하나이며, 2020년 Google scholar metrics 기준, 모든 학문 분야에서 5위를 차지하였다. (참고: Nature 1위, Science 3위). CVPR은 인공지능 학문 분야에서 ICCV, ECCV, NIPS, ICML, ICLR 및 AAAI와 더불어 매우 저명한 최상위 학회이다. 이 학회들은 대부분의 Top 저널들보다 경쟁력이 있는 것으로 알려져 있다.

한편 오태현 교수는 2020.2.14일 포스텍 전자과에 부임하여 Machine Intelligence 연구실 (MILab)을 운영하고 있으며 현재 기계 학습 및 이를 응용한 컴퓨터 비전 & 그래픽스 응용을 포괄하는 인공지능 분야 연구를 진행 중이다.

[삼성SDI] 2020년 박사/장학생 채용

[삼성SDI] 2020년 박사 / 장학생 채용

●지원기간 : 2020년 7월22일(수)~2020년7월31일(금)

●모집분야 : 화학, 화공, 재료, 기계, 전기전자 및 관련 전공

-Module/Pack 개발(열관리 및 열유동 해석, 구조해석)

-Module/Pack 개발(BMS S/W 개발)

●근무지역 : 기흥

●지원방법 : 이력서 또는 별도 지원서 양식 Email 접수

-접수처 : Email : keeyeoub.na@samsung.com / Tel : +82-31-288-4782

-지원서 : 다운로드 삼성SDI홈페이지 참고(https://www.samsugsdi.co.kr/career/index.html)

★ 연구개발/모듈개발자 브이로그 : https://youtu.be/pKtA_WfhyXU / https://youtu.be/7oELWCGyHCI

연구개발 직무소개 : https://youtu.be/WEFxYQPkCgs

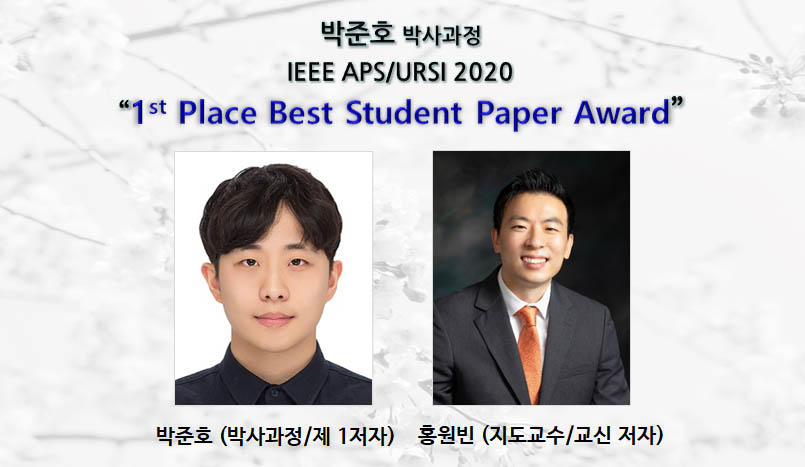

박준호(박사과정), IEEE APS/URSI 2020 “1st Place Best Student Paper Award”수상

포스텍 전자전기공학과 박사과정 박준호 씨 (논문지도: 홍원빈 교수)가 ’2020 IEEE International Symposium on Antennas and Propagation and USNC-URSI Radio Science Meeting (IEEE AP-S/URSI)'에서 우리 나라 역사상 최초로 ‘1st Prize Best Student Paper’를 수상하였다.

IEEE AP-S/URSI 는 국제전자전기공학회 전파 분과 (IEEE Antennas and Propagation Society/IEEE AP-S)에서 주관하는 세계 최대 규모의 국제 학술대회이다. 이번 2020 IEEE APS/URSI의 Student Paper Competition 분야에는 총 203편의 논문이 지원되었으며, 저자들은 본선에 오른 10명의 후보자 중 엄격한 4단계 심사를 거쳐 1위를 차지하는 성과를 거뒀다. 한편, 해당 저자들은 IEEE AP-S의 3대 학회 중 나머지 두 학회인 유럽 전역 최대 규모의 학회 (IEEE EuCAP 2020) 및 아시아 지역 최대 학회 (IEEE ISAP 2018)에서 각기 다른 주제로 1st Prize Best Paper Award를 수상한 바 있으며, 3대 학회 석권은 국제전자전기공학회 전파 분과 (IEEE AP-S) 역사상 최초의 기록이다.

이번 학술 대회에서 저자들은 “Optically Invisible Touch Sensor Panel Integrated Antenna: Concept and Demonstration at mmWave Spectrum”이라는 주제의 논문을 발표하였다. 본 논문에서는 광학적 비 가시성, 촉각 감지 및 무선 신호 송/수신 기능성을 갖춘 최초의 주파수 선택적 센서 개념을 제안하였으며 이를 상용 디바이스의 유기발광 다이오드 (OLED) 디스플레이에서 구현 및 내장하여 QHD+ 화질의 영상 출력과 함께 터치 감지 테스트 및 밀리미터파 5G 빔포밍 기술 시연을 선보였다. 본 연구의 신규성, 우수성 및 전파, 디스플레이, 신소재, 반도체 공학을 아우르는 다 학문적 특수성 등이 높이 평가되어 우수 논문상에 선정되었다.

백록현 교수, 2020년도 기초연구실(Basic Research Lab: BRL) 돌파형 신규과제 선정

- 백록현 교수 (포스텍 전자전기공학과)가 과학기술정보통신부에서 지원하는 기초연구실 (Basic Research Lab: BRL) 돌파형 과제에 선정되어 3+3년간 연구협약 (5억/year)을 맺고, ‘3D-NAND Flash의 초고난도 산업 난제 해결을 위한 융합형 메모리 AI 플랫폼 개발'이라는 주제로 연구를 수행한다.

연구팀은 최현철 교수(영남대학교), 박민상 박사(SK hynix), 윤준식 연구조교수(포스텍)로 구성되어 있으며, 3D-NAND 메모리 공정/소자/전산모사/AI 전문가들의 유기적 협업을 통해 최첨단 3D-NAND Flash의 난제를 근본적으로 해결하고 이를 메모리 산업에 신속하게 적용하는 것을 최종 과제 목표로 한다.

기초연구실–돌파형 과제

기초연구실 사업내 돌파형 과제는 ‘주력산업 분야의 핵심기술 확보 및 자립화 등을 위한 기초연구를 지원하여 과학기술 현안의 근본적 해결 기반을 마련’하는 것을 사업 목표로 한다.