새로운소식

학과의 최신 소식과 활동을 전해드립니다.

김병섭 교수 연구팀 “IEEE OJ-SSCS”초청 논문 (Invited Paper) 게재

포스텍 전자전기공학과 김병섭 교수 연구팀[통합과정 문창재, 박사 졸업생 최민수(현 Marvell Technology), 이명국(현 삼성전자)]이 반도체 집적회로 분야의 신생 저널인 OJ-SSCS (Open Journal of the Solid-State Circuit Society)에 초청 리뷰논문을 게재하며 국제적으로 연구 성과를 인정받았다.

OJ-SSCS는 IEEE SSCS (Solid-State Circuits Society)에서 2020년에 설립한 오픈 액세스 저널로, 집적회로의 트랜지스터 수준 설계에 특히 중점을 둔 solid-state 회로 분야의 학술지이다. 특히 이번 초청은 신생 저널인 OJ-SSCS의 학술적 위상을 높이기 위해 각 분야의 선도적인 연구진들을 엄선하여 이루어졌다는 점에서 의미가 크다.

연구팀이 발표한 "Review on Resistive Termination Techniques Driven by Wireline Channel Behaviors" 논문은 고속 데이터 전송 시스템의 설계에 필수적인 resistive termination 기술을 종합적으로 분석하고, 설계 방법론을 체계적으로 정리한 리뷰 논문이다. 특히 연구팀이 개발한 ‘relaxed impedance matching’ 기법은 기존의 엄격한 impedance matching 조건을 완화하면서도 신호 품질을 유지할 수 있는 방법론으로, 설계자들에게 더 큰 자유도를 제공하여 실용적 가치가 높다고 평가받았다.

이상욱 (박사과정), 대한전자공학회 2024 추계학술대회 ‘우수 논문상 ‘ 수상

포스텍 전자전기공학과 박사과정 이상욱 학생 (지도교수: 백록현 교수)이 대한전자공학회가 주관하는 ‘2024추계학술대회’에서 “초고성능 및 초고집적이 가능한 패턴 유전체 절연 벽을 갖춘 2nm 노드 나노시트 전계 효과 트랜지스터” 논문을 발표하여 우수 논문상 (상금: 100 만원)을 수상하였다.

본 논문에서는 패터닝된 유전체 벽을 소자 사이에 도입하여, 기존의 로직 소자에서 스케일링이 불가능했던 영역의 길이를 획기적으로 줄일 수 있는 소자 구조를 처음으로 제시하였으며, 제안된 소자구조의 유전체벽의 구조 최적화를 통해 반도체 소자의 대표 특성인 power/performance/area (PPA)을 모두 개선할 수 있었다.

대한전자공학회 추계학술대회는 반도체, 통신, 컴퓨터, 인공지능 신호처리, 시스템 및 제어, 산업전자, new emerging area 총 7개의 분야로 구성된 학술대회로, 2024 추계학술대회에는 약 360여편의 논문과 강연이 발표되었다. 우수 논문상은 발표된 논문 중 높은 평가와 발표 점수를 합산하여, 우수한 논문을 발표한 학생에게 수여된다. 시상식은 2024년 11월 22일 하이원 리조트에서 개최된 2024 추계학술대회에서 진행되었다.

신세운 교수 연구팀 “전력전자학회 우수논문상“ 수상

신세운 교수 연구팀 “전력전자학회 우수논문상“ 수상

포스텍 반도체대학원 박사과정 김종훈 학생과 전자전기공학과 신세운 교수의 전력관리 및 집적회로 시스템 설계 연구실(PICTUS)이 국내 전력전자학회에서 주최한 2025 추계 학술대회에서 “과전류, 과전압 보호회로를 동시에 내장한 질화갈륨 전력반도체용 게이트 구동회로”를 주제로 “우수논문상"을 수상하였다.

본 논문은 질화갈륨(GaN)을 포함한 와이드 밴드갭(WBG) 화합물 반도체의 고속 및 높은 신뢰성의 전력변환을 위한 게이트 구동회로 설계를 제안하였다. 제안하는 질화갈륨 화합물 전력반도체 특화 게이트 구동회로는 고속 게이트 구동 IC를 활용하여 최대 13.56MHz 동작을 수행하였으며, 120ns의 과전류 보호시간과 45%의 게이트 전압 피크 저감을 달성하였다. 이를 통해 가전기기, 전기자동차, 청정에너지 등 다양한 응용처의 소형화와 동작 신뢰성을 확보할 수 있을 것으로 기대된다.

김명훈(박사과정), 이혜구(통합과정), 김동건(통합과정) 한국물리학회 우수발표상 수상

전자전기공학과 이문주 교수 연구실의 박사과정 김명훈 학생, 통합과정 이혜구 학생, 통합과정 김동건 학생이 2024년 가을학술논문발표에서 우수발표상을 수상하였다. 김명훈 학생은 포획된 이온의 정렬-무질서 전이에 대한 실험 연구, 이혜구 학생은 이온 큐비트의 냉각과 얽힘(entanglement) 상태 생성, 김동건 학생은 중성 원자 큐비트를 광공진기내에 광격자 기술을 이용하여 포획한 실험 연구를 발표하였다. 본 논문발표회의 원자분자물리분과에서 총 6편의 우수발표상이 수여되었고, 이문주 교수 연구실은 그 중 3개의 상을 수상하였다.

이동섭 IEEE MTT-S Asia-Pacific Microwave Conference (APMC) 2024” Honorable Mention of Best Paper Award 수상

포스텍 전자전기공학과 통합과정 이동섭 학생 (공동 1저자, 지도교수 : 홍원빈 교수)이 2024 IEEE MTT-S Asia-Pacific Microwave Conference (APMC)에서 “A Study on the Influence of Metal Mesh Design on a Transparent Antenna on Display for Radar and Communication Using Ultra Fine Mesh Film”이란 주제로 “Honorable Mention of Best Paper Award”를 수상하였다. 아울러, 이번 수상은 해당 연구 그룹이 APMC 학회에서 거둔 첫 번째 수상이다.

IEEE Asia-Pacific Microwave Conference (APMC)는 IEEE 전파/회로 분야 (IEEE Microwave Theory and Techniques Society/IEEE MTT-S)의 아시아-태평양 전역에 전파, 마이크로, 밀리미터파 및 관련 기술 분야의 연구자와 엔지니어들이 모이는 최대 규모의 국제학술대회로서 올해는 인도네시아, 발리에서 개최되었다.

이번 학술대회에서 발표된 논문은 초미세공정인 금속 Mesh Film을 활용한 투명 안테나 설계의 혁신성을 중심으로, 레이더 및 통신 시스템에서의 차세대 응용 가능성을 제시하며 큰 주목을 받았다. 특히, 본 연구는 금속 Mesh 설계가 투명 안테나의 성능 및 통합형 디스플레이 기술에 미치는 영향을 체계적으로 분석함으로써, 차세대 통신 및 레이더 기술의 발전에 기여할 잠재적 영향력에 대한 가치가 높이 평가되어 Honorable Mention of Best Paper Award 수상에 선정되었다.

신세운 교수 연구팀 “ISSCC 2025”논문 채택 & SRP 선정

포스텍 반도체대학원 박사과정 김종훈 학생과 전자전기공학과 신세운 교수의 전력관리 및 집적회로 시스템 설계 연구실이 International Solid-State Circuit Conference (ISSCC) 2025에 반도체 회로설계 연구 결과를 선보인다. 포스텍 전자전기공학과 통합과정 조문정 학생의 연구 결과 또한 ISSCC Student Research Preview (SRP)를 통해 발표할 예정이다.

김종훈 학생은 생체 이식형 의료기기의 무선충전 기술 중 하나인 공진형 전류모드의 파라미터 최적화 및 전력 수신 코일 다차원화를 최초로 달성하였다. 해당 논문의 제목은 “A Programming-Free Three-Dimensional Resonant Current-Mode Wireless Receiver with Real-Time Link-Adaptivity and a 0.904 cm3 Receiver Coil for Implantable Systems”이다.

또한, 조문정 학생은 단일 스테이지 및 단일 변압기 권선으로 다중 출력을 제공하는 온칩 절연형 오프라인 RGBW LED 드라이버를 처음으로 제안하였으며, 독립적이고 정밀한 전류 제어가 가능한 새로운 제어기를 설계하였다.

ISSCC는 “세계 반도체 설계 올림픽”으로 불리며, 70여년 전통의 반도체 회로설계 분야 최고 권위 학회이다. ISSCC 2025는 내년 2월 16일부터 20일까지 미국 샌프란시스코에서 진행된다.

윤주영 박사과정, 삼성디스플레이 산학협력 논문대회 대상 수상

전자전기공학과 박사과정 윤주영 학생(공저자: 강도완, 지도교수: 정윤영)이 ‘삼성디스플레이 산학협력 논문대회’에서 대상을 수상했다.

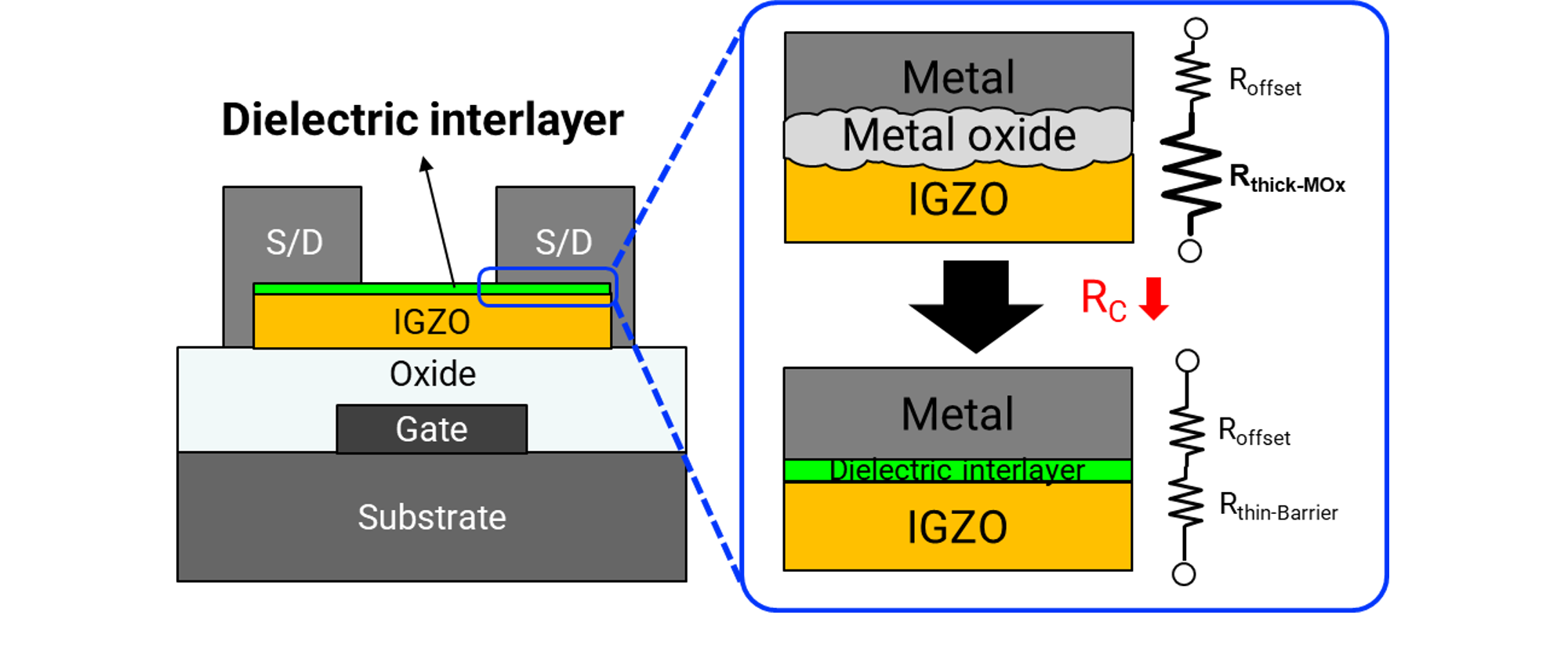

수상 논문"Improving Contact Resistance and Thermal Stability of Sub-µm a-IGZO Transistors for Next-Generation Displays"에서는 차세대 고해상도 디스플레이 구현을 위한 핵심 기술인 산화물반도체/금속 인터페이스의 접촉 저항과 열적 안정성을 동시에 향상시키는 새로운 접근 방안을 제안하였다.

산화물 반도체는 다양한 장점으로 인해 디스플레이 산업에서 사용되고 있지만, 실리콘 소재에 비해 낮은 전자 이동도와 높은 접촉 저항으로 인해 화소 밀도가 높은 차세대 디스플레이에는 적용이 어려웠다.

본 연구에서는 산화물 반도체와 금속 사이에 확산을 막아주는 초박막 절연층을 삽입하여 계면에서의 금속 산화물 형성을 효과적으로 차단하는 방법을 제안했다. 이를 통해 접촉 저항을 개선하여 short channel 소자의 전기적 특성을 효과적으로 개선했고, 동시에 열에 의한 트랜지스터 성능 저하를 최소화하여 디스플레이 소자의 장기적인 안정성 및 고해상도 구현에 기여하는 중요한 기술적 진전을 이루어 높은 평가를 받았다.

이동섭 2024 IEEE ISAP (Sponsored by IEEE AP-S TCAM)” 1st Prize Best Antenna Measurement Paper Awards 수상

포스텍 전자전기공학과 통합과정 이동섭 학생 (지도교수 : 홍원빈 교수)이 2024 IEEE International Symposium on Antennas and Propagation (ISAP)에서 “Streamlined Characterization Methodology for Chip-Level Antenna Performance : Electrical and Mechanical Analysis and Optimization”이란 주제로 “1st Prize Best Antenna Measurement Paper Awards”를 수상하였다. 아울러, 이번 수상은 해당 연구 그룹이 ISAP 학회에서 최초로 거머쥔 수상이다.

IEEE International Symposium on Antennas and Propagation (ISAP)는 IEEE 전파 분야 (IEEE Antennas and Propagation Society/IEEE AP-S)의 아시아-태평양 전역에 최대 규모의 국제학술대회로서 올해는 한국 인천 송도에서 개최되었다. 이번 ISAP 2024에서는 총 516편의 논문이 기고 되었고, 엄격한 3단계 심사를 거쳐 최종 후보 6편 중 1위로 수상하는 성과를 거뒀다.

이번 학술대회에서 발표된 논문은 Fan-Out Wafer Level Package (FOWLP) 기반 안테나 설계에서 발생하는 Die-shift 및 Warpage와 같은 다중 물리 기반의 전기적, 기계적 특성 분석 실험을 통해 정밀한 성능평가 방법을 제안하며, 이를 실험을 통해 검증하였다. 본 연구는 독창성과 혁신성, 그리고 Chip Level에서의 안테나 패키징 및 전자기파 응용 분야에 미칠 잠재적 영향력에 대한 가치가 높이 평가되어 Best Antenna Measurement Paper 1위에 선정되었다.

백록현 교수 IEEE VLSI Symposium Technical Program Committee 선정

포스텍 전자전기공학과 백록현 교수가 IEEE VLSI Symposium Technology and Circuit 학회의 Technical Program Committee로 선정됐다.

올해로 44주년을 맞이한 Symposia on VLSI Technology and Circuits는 International Electron Device Meeting(IEDM)과 함께 반도체 소자/공정 분야에서 세계 최고의 권위를 가진 양대 학회 중 하나로, 매년 미국과 일본을 오가며 개최된다. 학회에서는 매년 반도체 기술 분야의 최신 연구 내용을 발표하고, 전 세계 반도체 기업과 학계에서 투고한 논문 중 가장 뛰어난 소수의 논문을 선정한다.

백록현 교수는 최첨단 로직 소자인 Gate-All-Around Nanosheet FET(GAA NSFET) 및 Complementary FET(CFET)과 3DIC에 적합한 새로운 배선 기술 중 하나인 Backside Power Delivery Network(BS-PDN)간의 접목 기술 개발 및 평가에 기여할 것으로 기대된다.

남기훈 (박사과정), 제 8회 K-CHIPS Awards ‘우수 학생연구원 선정’

포스텍 전자전기공학과 박사과정 남기훈 학생(지도교수: 백록현 교수)이 산업통상자원부, 한국산업기술평가관리원(KEIT), 한국반도체연구조합(COSAR)이 주관하는 민관공동투자 반도체고급인력양성사업(2023~2032)의 “초고층 3D NAND 메모리를 위한 고이동도 채널/유전막 신소재 개발 및 AI 기반 대규모 해석 플랫폼 구축” 프로젝트를 수행하고, ‘제 8회 K-CHIPS(Korea Collaborative & High-tech Initiative for Prospective Semiconductor Research) Awards’에서 우수 학생연구원(상금: 200만원)으로 선정되었다.

본 Awards는 민관공동투자 반도체고급인력양성사업 참여 학생연구원의 역량 강화와 동기부여를 위해 진행되며, 학생연구원의 연구 성과와 본 사업의 기여도 평가를 통해 수상자를 선정한다. 이번 시상은 현재 본 사업의 과제를 진행 중인 총 94개의 참여연구기관 가운데 성과가 우수한 7개의 기관에게 수여되었으며, 백록현 교수 연구팀은 제 3~7회 K-CHIPS Awards에 이어 6회 연속 수상하였다.