[월:] 2018년 07월

삼성전자 DS부문 육목 SW 알고리즘 대회 홍보

국가과제_분할예산편성표(양식)

연구참여확약서

국가연구개발사업 연구참여확약서

㈜아나패스 신입 및 경력 사원 모집(전문연구요원 지원 가능)채용공고

당사는 2002년말 아날로그 및 디지털 회로 설계기술을 기반으로 설립한 팹리스(fabless) 반도체 설계기업으로 2010년 11월 코스닥에 상장하였습니다

당사는 주로 LCD 3D TV, 스마트 TV와 같은 디스플레이 제품과 태블릿, 스마트폰과 같은 핸드셋 단말기에 들어가는 반도체 칩 제품을 설계, 제작하고 있으며, 동 산업 내에서 기술 표준을 선도하는 등 탁월한 기술역량을 보유하고 있는 High-tech 중소기업입니다.

현재 삼성전자, LG전자, 소니 등 국내외 유명 디스플레이업체, TV 셋트업체 및 핸드셋 제조업체 등에 반도체 칩 제품과 핵심 기술을 공급하고 있으며, 우수한 인력, 유연하고 창의적인 조직문화, 건실한 재무구조를 바탕으로 고속으로 성장하고 있습니다.

금번, 당사에서는 신규 사업 확장 및 사업 다각화를 위해 하기의 역량을 갖춘 재원을 모집하오니, 많은 관심과 지원 부탁 드립니다.

[기업 개요]

- 업종 : 반도체 설계

- 상장여부 : 코스닥 상장 (2010년 11월)

- 임직원수 : 약 130명

- 위치: 서울 구로디지털 단지 내

- 2015년 매출액 : 2017년 매출액 870억

[모집부문 및 자격요건]

| Job Position | SoC 설계 연구원 |

| Job Description | l ASIC 설계 및 설계 검증

l ME/MC/Image Compression |

| Requirement Skills

& Experience |

(필수)

1) 관련 전공 학사 혹은 석사졸업 신입 or 개발 경력 최소 2년 이상 경력자 2) Microprocessor, BUS, Peripheral 등으로 이루어진 Digital System의 architecture를 Design 할 수 있는 능력 보유 3) Low power 설계에 대한 Knowhow 보유 4) Microprocessor 에 대한 깊은 지식 보유 (우대) 하기 Tool 사용 가능자 |

| Tools | 1) Coding : Verilog, VHDL

2) Simulator : Ncsim, Verilog-XL, Model Sim 3) Synthesis : Design, HDL, DFR Complier 4) DFT & Lint : Tetra-max, Spy-Glass 5) Formal : Formality, Conformal 6) STA : Prime-time, Time Craft 7) FPGA : Synplicity, Xilinx & Altera 용 FPGA Complier 8) Others : Verdi, VC++ |

[지원 안내]

- 전형절차 : 서류 -> 면접전헝 (1차) -> 면접 (2차, 생락될 수 있음)

- 접수방법 : 홈페이지 온라인 이력서 접수 (당사 이력서 양식 다운로드 후 파일첨부)

- 제출서류 : 이력서, 자기소개서 각 1부

- 담 당 자 : 인사탐 황하영 대리 (연락처 : 02-6922-7304 /recruiting@anapass.com)

- 홈페이지 : www.anapass.com

- 제출기한 : 2018년 7월 11일 ~ 2018년 10월 31일

- 선착순 수시면접으로 마감일 이전에 사전 마감이 될 수 있습니다.

- 근무조건 : 주5일 근무제

- 급 여 : 당사 내규에 따름 (동종 업계 대비 최상위 대우)

복리후생 : 자기계발비, 식대, 교통비, 건강검진비, 명절선물, 각종 경조금/휴가, 사내 동호회비 지원, 대체휴가제도 등

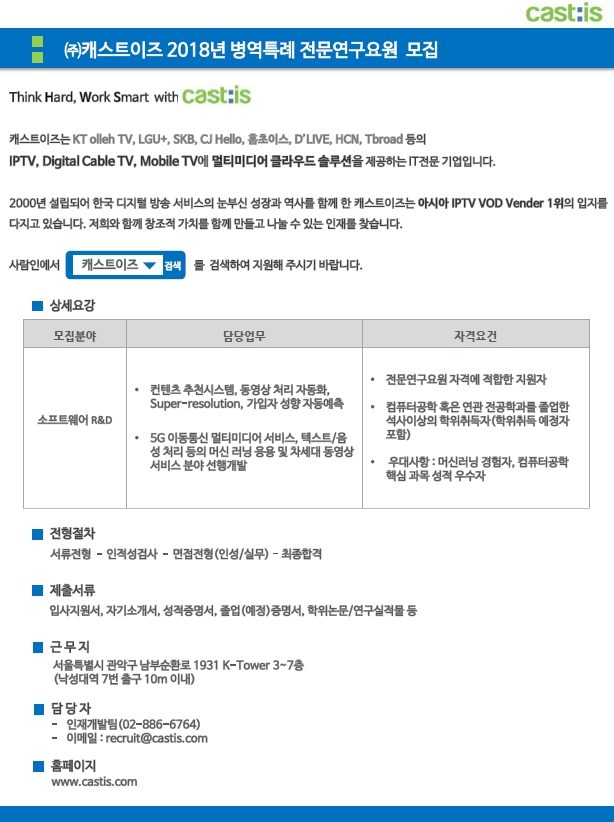

(주)캐스트이즈 채용공고

윤인열, 대한전자공학회 (IEIE) 하계종합학술대회 “우수 논문상” 수상

포스텍 전자전기공학과 대학원 윤인열 학생(advisor: 정윤영 교수)이 2018년도 대한전자공학회 (IEIE) 하계종합학술대회에서 우수논문상을 수상하였다.

논문 제목: “영아 돌연사 증후군 예방을 위한 저전력 무선 웨어러블 센서”

윤인열 학생은 영아 사망의 주요 원인인 영아 돌연사 증후군(sudden infant death syndrome, SIDS)을 예방하기 위한 저전력 무선 웨어러블 센서 시스템을 발표하였으며, 이를 이용하여 자세 조절이나 의사소통이 원활하지 않은 영아의 건강을 보호자가 편리하게 관리할 수 있는 방안을 제시하였다.

대한전자공학회는 70여년의 역사를 갖는 ICT분야 국내 최대 학회이며, 이번 하계종합학술대회에서는 16대 1이 넘는 경쟁률 속에 우수상이 수여되었다.

김병섭 교수, “IDEC 우수 참여교수상 수상”

2018년 7월 3일 IDEC Congress에서 포스텍 전자전기공학과 김병섭교수가 2017년 IDEC 우수 참여교수상을 수상하였다.

반도체설계 교육센터(IC Design Education Center: IDEC)는 1995년에 설립되어, 산업기반이 취약한 비 메모리분야의 국가 경쟁력강화를 위해, 매년 전국 대학의 참여교수에 대한 지원을 통해 우수 설계 인력을 양성하는 사업을 수행한다.

IDEC은 사업의 일환으로 매년 성과가 우수한 참여교수를 선정하여, 그 다음해 IDEC 우수 참여교수상을 시상하고 있다.

이시현 교수팀 IITP과제 선정

포스텍 전자전기공학과 이시현, 이남윤, 이영주 교수팀 (DGIST 이제민 교수 포함)은 “Massive IoT 네트워크를 위한

저전력 · 저지연 물리계층 보안기술”의 주제로 과학기술정보통신부 산하 정보통신기술진흥센터에서 주관하는 혁신도약형 R&D 과제에 선정되었다.

이시현 교수팀은 사물인터넷을 위한 물리계층기반 인증 및 보안 송수신 기술을 연구할 예정이다.

총 연구기간: 2018.07.01 ~ 2022.12.31

지원금액: 1단계 5억원, 2단계(선정 시) 15억원

김상우 교수, 심재윤 교수 “2018 포스텍 대표연구성과 선정”

우리 대학에서 선정한 올해의 대표연구성과 20선 중 전자전기공학과 김상우 교수의 ‘전동기 사고 예방을 위한 조기고장진단 알고리즘‘과 심재윤 교수의 ’초저전력 단일칩 무선 센서 노드‘의 연구가 각각 선정되었다.

김상우 교수의 연구는 기존의 전동기 고장진단의 한계점인 약한 고장에 대한 진단을 용이하게 할 뿐 아니라 동작조건에 영향을 받았던 기존 고장지표들의 한계 또한 극복하여 발전소, 공장 및 동작조건이 지속적으로 변하는 전기자동차 분야까지 활용할 수 있게 되었다.

심재윤 교수의 연구는 다양한 초소형 나노/바이오 센서와 결합하여 초소형 헬스케어를 위한 융합 연구에서 세계적인 연구 성과를 낼 수 있는 바탕이 되었으며, 현재 개발된 칩을 적용하여 초경량 개인용 유해가스 감지 시스템의 사업화에도 동시에 진행 중에 있다.