[월:] 2018년 06월

황석하(석사과정),“ Best Design Award”수상

포스텍 전자전기공학과 석사과정 황석하씨(논문지도: 이영주 교수)가 반도체설계교육센터(IDEC)가 주관하는 2018 IDEC Congress Chip Design Contest에서 “Energy efficient symmetric block-wise concatenated BCH decoder for healthy mobile systems”란 설계로 Best Design Award 를 수상하였다.

황석하씨는 NAND 플래시 메모리 기반의 저장매체의 신뢰성을 극대화 할 수 있는 새로운 구조의 오류정정부호를 제안하고, 이를 가장 효율적으로 지원하는 세계 최고수준의 초고속 초저전력 decoder 구조를 구현하였다.

IDEC은 95년 산업통상자원부의 지원으로 설립되어 매년 300여건의 시스템 반도체 칩의 설계를 지원하고 있으며, 가장 뛰어난 설계를 선정하는 Chip Design Contest를 매년 개최하고 있다. 올해 진행된 IDEC Congress에는 총 120여건 이상의 설계가 출품되었으며 이중 디지털 분야에서 황석하씨의 설계가 최고 수상의 영예를 안았다.

[ETRI] 융복합센서연구그룹 인재 모집

[ETRI] 융복합센서연구그룹 인재 모집

안녕하세요?

저는 포항공대 신소재공학과 1기생(1987 학부 입학, 동학과 석사/박사 졸업)으로

현재 한국전자통신연구원(ETRI)에서 근무하고 있는 양우석입니다.

제가 근무하고 있는 ETRI 융복합센서연구그룹에서 전기전자공학 전공한 인재를 모집하고 있는데,

포항공대 전기전자공학과에 관련 내용을 홍보해주셔서 좋은 학생이 지원할 수 있도록 부탁드립니다.

병역특례 대상자 및 병역 면제/필 일반 정규직 지원자 모두 가능합니다.

저희 그룹이 ETRI에서 근무 여건/분위기가 가장 좋은 편에 속하니 적극 추천하셔도 됩니다.

관심있는 학생은 저나 담당 PL인 이형근 박사(포항공대 화학과 1994학번, 010-6641-5352, hklee@etri.re.kr)에게 문의하면 됩니다.

감사합니다.

—————————————————————————–

양우석(Woo Seok Yang)

책임연구원/공학박사

한국전자통신연구원 ICT소재부품연구소 융복합센서연구그룹

305-700 대전시 유성구 가정로 218

E-mail: wsyang68@etri.re.kr / Office: 042-860-1675 / Mobile: 010-9754-1539 / Fax: 042-860-5608

[Skelter Labs] 스켈터랩스 채용 공고

Software Engineer (신입/경력/전문연구요원)

언제 어디서나 우리의 일상을 이해하고, 도와주고, 더 나아지게 하는 머신 인텔리전스의 혁신을 이룬다. 우리의 Mission입니다.

각 팀마다 다양한 배경의 재능 있는 멤버들로 구성된 스켈터랩스는 인간의 지능을 근간으로 인간을 위한 Machine Intelligence를 만드는 데에 주력하고 있습니다.

휴대폰, 자동차, 음성인식 스피커 등 종류를 막론하고, 사용자에게 맞춰 개인화되고, 상황을 인지 하며 자연스럽고 감정적인 소통을 할 수 있는 진정한 Intelligence 기술을 만드는 것이 목표입니다.

Google, Nexon, Yahoo, Naver 등 다양한 배경을 가진 인재들이 하나의 프로젝트가 아닌 다양한 프로젝트에 참여하며 인공지능 기술로 세상을 disrupt 하는 서비스를 만드는데 열정을 바치고 있습니다. 뿐만 아니라, KAIST AI Lab 출신 박사, 개발자들과 함께 인공지능 기술 고도화 목표를 향해 달리고 있습니다.

홈페이지 및 보도자료:

l 홈페이지: www.skelterlabs.com

l 블로그: http://www.skelterlabs

l 페이스북: https://www.facebook.

l 보도자료: 스켈터랩스 누적 투자 100억 달성 매일경제–조원규 사장님 인터뷰

역할 및 근무방식

l 적극적인 기획 참여. 팀원 모두가 아이디어 브레인스토밍 및 정기적인 Demo Day를 진행합니다. Product Manager(PM)는 이렇게 나온 기획 아이디어들을 수집, 정리해서 하나의 완성된 기획으로 만듭니다.

l 함께하는 Architecture Design. 시니어 엔지니어들이 중심이 되어서 서비스의 전체적인 아키텍처를 디자인하고, 각 서브시스템들은 시니어들의 리뷰 하에 최대한 주니어들이 중심이 되어서 디자인을 진행합니다. 이렇게 design doc이 완성됩니다.

l 소프트웨어 구현. 모든 코드는 항상 한 명 이상의 코드 리뷰를 통과한 뒤 제출됩니다. 코드리뷰는 절대 형식적으로 진행되지 않습니다. 간단하게는 코딩 스타일, 오타, 코멘트가 잘 이해할 수 있을 만큼 작성 되었는지 부터 시작해서, 버그, 보안 이슈, 레이스 컨디션, 예외 케이스 등을 상호 간에 확인하고, 유닛 테스트 및 통합 테스트 코드가 일반적인 케이스 및 예외 케이스들을 잘 커버하고 있는 지까지 전방위 적인 리뷰를 진행합니다. 주니어들은 시니어들과의 리뷰를 통해 시니어 레벨의 코드를 작성하게 되고, 빠른 시간 내에 실력 향상을 이룰 수 있습니다.

l 서비스 구현 뿐만 아니라, 서비스 유지보수를 돕거나 자동화하는 툴도 마찬가지로 prioritize해서 개발합니다.

자격요건

l 컴퓨터 과학이나 비슷한 분야 (전산, 전자, 수학 등) 학사 이상, 혹은 동등 이상의 경력

l 다음 중, Senior의 경우 2개, Junior의 경우 1개 이상의 Programming Language 구사

– C++, JAVA, Javascript, Python

l 전문연구요원의 경우 석사 학위 이상 소지자로 대한민국 병역법 상 전문연구요원 근무 가능한 분

우대사항

l 컴퓨터공학이나 비슷한 분야 (전산, 전자, 수학 등) 석사 및 박사 학위

l Android, iOS 등 모바일 환경에서 동작하는 실제 App 제작 경험

l TensorFlow, PyTorch 같은 Framework를 이용한 Machine Learning

l MapReduce나 Spark 같은 Distrib

l 자연어 처리

l RDB(MySQL 등)나 NoSQL DB(MongoDB, Redis 등) 개발 경험

구비서류 및 지원방법

l 자유양식의 국영문이력서 및 자기소개서

l 이메일: recruit@skelterlabs.co

l 연봉: 회사내규

면접 절차

l 서류전형

l 1차 Online 기술면접(평가항목 1. 알고리즘

l 2차 Onsite 기술면접 (평가항목 1. 알고리

l 3차 대표이사 면접

[보잉코리아 채용] 공학계열 관련 채용공고

|

Good afternoon.

The purpose of my email today is to engage your team assistance to communicate our Boeing Korea’s engineering positions to the alumni of your university.

Here is the website hyperlink for your student reference and to submit their application online.

Boeing Korea Engineering Positions

We believe that this is a great opportunity that should not be miss & appreciate your help to post this job into your university student portals or job boards.

Thank you very much in advance.

|

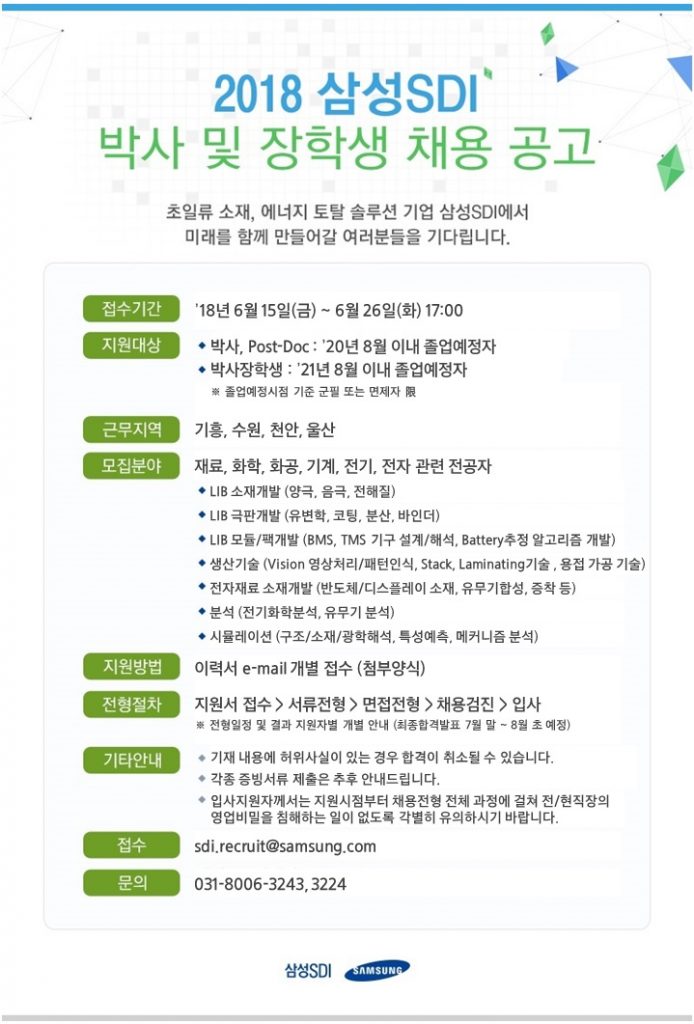

[삼성SDI] 박사 및 장학생 채용 공고

[삼성SDI] 박사 및 장학생 채용 공고

김병섭 교수팀 기초연구실과제 선정

포스텍 전자전기공학과 김병섭, 최준일, 홍원빈, 정윤영, 이영주 교수팀은 “실시간 고해상도 in-vivo imaging을 위한 초고속 체내 데이터 전송기술”의 주제로 11.6:1의 경쟁을 뚫고 정보통신부 집단연구지원사업(기초연구실)에 선정되었다.

김병섭 교수팀은 다학제적 연구를 통해 생체내의 고해상도 영상정보를 실시간으로 체외로 전송할 수 있는 초고속 전송기술을 연구할 예정이다.

연구기간: 2018.06-2021.02

지원금액: 13억 7천500만원

김환진 (석사과정), “Qualcomm IT Tour 프로그램”선정

포스텍 전자전기공학과 석사과정 김환진씨(논문지도: 최준일 교수)가 2018년도 Qualcomm IT Tour 16기 프로그램 참가자에 최종 선발되었다.

이번 16기 Qualcomm IT Tour 프로그램은 전국 이공계 학부, 석사과정학생을 대상으로 제안서를 제출 받아 최종적으로 20명을 선발하였다.

김환진씨는 “5G 유스케이스(use case)에 대한 제안”을 제출하여 최종 선발되었으며 6월 25일 부터 7월 1일 (4박 7일) 동안 Qualcomm 미국 본사를 방문하게 된다.